# **Combinational Building Blocks**

Joannah Nanjekye

July 16, 2024

◆□▶ ◆□▶ ◆臣▶ ◆臣▶ 臣 のへぐ

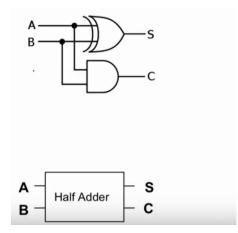

# A Half Adder

- Add two bits A and B

- Output the sum S

- Output the carry C

< □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □

| Α | В | C | S |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

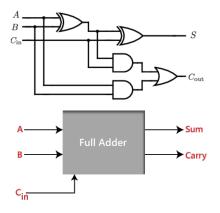

# A Full Adder

- Add three bits A, B, and C<sub>in</sub>

- Output the sum S

- Output the carry Cout

| Α | В | C <sub>in</sub> | Cout | S |

|---|---|-----------------|------|---|

| 0 | 0 | 0               | 0    | 0 |

| 0 | 0 | 1               | 0    | 1 |

| 0 | 1 | 0               | 0    | 1 |

| 0 | 1 | 1               | 1    | 0 |

| 1 | 0 | 0               | 0    | 1 |

| 1 | 0 | 1               | 1    | 0 |

| 1 | 1 | 0               | 1    | 0 |

| 1 | 1 | 1               | 1    | 1 |

▲□▶ ▲□▶ ▲□▶ ▲□▶ = 三 のへで

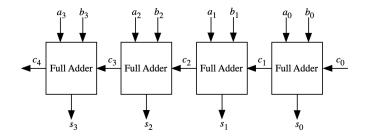

## A 4-bit Adder

- Constructed with full adders connected in cascaded

- Carry output from each adder is connected to the carry input of the next adder in the chain

- Carry input is from the least significant bit (LSB)

- The sum output is represented by the bits s<sub>0</sub>-s<sub>3</sub>

# **Ripple Carry Adder Delays**

- An output sum and carry is determined after the carry created from the previous stages is produced

- The sum of the MSB is known after the carry signal has rippled through the adders from the LSB

- Final sum and carry bits will be valid after a considerable delay

$Sum_{s_{n-1}} delay = 4n + 2$  $Carry_{c_n} delay = 4n + 3$

(ロ) (同) (三) (三) (三) (○) (○)

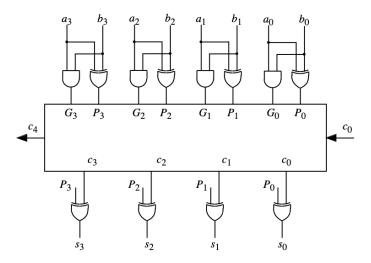

## Carry Lookahead Adder (CLA)

Calculate the carry signals in advance, based on the input signals

# Carry lookahead adder (CLA)

Assumes a carry signal can be generated in two cases:

- When both bits are 1

- When one of the two bits is 1 and the carry-in is 1

- We can therefore write the equations:

$$C_{i+1} = G_i + P_i \cdot C_i$$

$S_i = P_i \oplus C_i$

$$G_i = a_i \cdot b_i$$

$P_i = a_i \oplus b_i$

< □ > < 同 > < 三 > < 三 > < 三 > < ○ < ○ </p>

Advantages and Disadvantages of Carry Look-Ahead Adder

Advantages:

- The propagation delay is reduced

- It provides the fastest addition logic

Disadvantages:

The Carry Look-ahead adder circuit gets complicated as the number of variables increase

(ロ) (同) (三) (三) (三) (○) (○)

The circuit is costlier as it involves more number of hardware

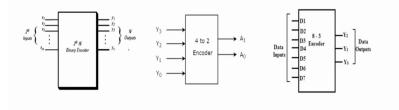

### Decoders

- A decoder selects one of 2<sup>n</sup> outputs according to an encoded input (n bits)

- Only one of the outputs is asserted based on the combination of inputs present

- When the decoder is enabled

- When an "enable" input, enable = 0 then all outputs are 0

◆□▶ ◆□▶ ▲□▶ ▲□▶ ■ ののの

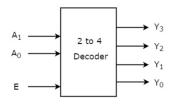

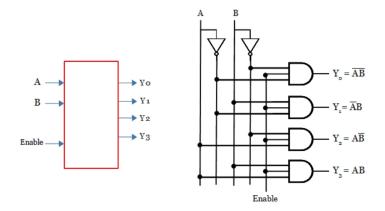

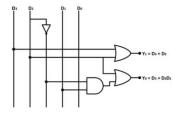

## 2 to 4 Decoder

The outputs of the decoder are the min terms of *n* input variables lines, when it is enabled

| Ε | Α | В | $Y_0$            | $Y_1$ | $Y_2$ | $Y_3$ |

|---|---|---|------------------|-------|-------|-------|

| 0 | Х | Х | 0                | 0     | 0     | 0     |

| 1 | 0 | 0 | 0                | 0     | 0     | 1     |

| 1 | 0 | 1 | 0<br>0<br>0<br>0 | 0     | 1     | 0     |

| 1 | 1 | 0 | 0                | 1     | 0     | 0     |

| 1 | 1 | 1 | 1                | 0     | 0     | 0     |

▲□▶▲□▶▲□▶▲□▶ □ のQ@

$Y_{3} = E \cdot A \cdot B$  $Y_{2} = E \cdot A \cdot \overline{B}$  $Y_{1} = E \cdot \overline{A} \cdot B$  $Y_{0} = E \cdot \overline{A} \cdot \overline{B}$

#### 2 to 4 Decoder

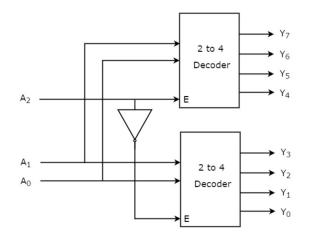

#### **Constructing Higher Order Decoders**

# of decoders =  $m_2/m_1$ # of 2 to 4 decoders = 8/2 for a 3 to 8 decoder

◆□▶ ◆□▶ ◆豆▶ ◆豆▶ □豆 の々で

#### Encoders

- A encoder is the inverse of a decoder

- It is not used frequently as decoders

## 4 to 2 Encoder

| HIGHEST | INP | UTS | LOWEST | OUTPUT |    |

|---------|-----|-----|--------|--------|----|

| D3      | D2  | D1  | D0     | YO     | ¥1 |

| 0       | 0   | 0   | 0      | Х      | Х  |

| 0       | 0   | 0   | 1      | 0      | 0  |

| 0       | 0   | 1   | X      | 0      | 1  |

| 0       | 1   | X   | X      | 1      | 0  |

| 1       | X   | X   | X      | 1      | 1  |

▲□ > ▲圖 > ▲目 > ▲目 > ▲目 > ④ < @ >

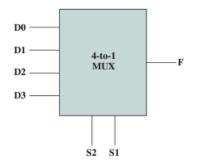

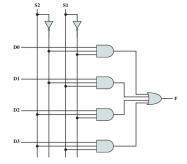

## **Multiplexer**

A multiplexer or mux is a device that selects one of several input signals and forwards the selected input into a single line

◆□▶ ◆□▶ ▲□▶ ▲□▶ □ のQ@

A multiplexer of 2<sup>n</sup> inputs has n select lines

# Multiplexer

| S2 | <b>S1</b> | F  |

|----|-----------|----|

| 0  | 0         | D0 |

| 0  | 1         | D1 |

| 1  | 0         | D2 |

| 1  | 1         | D3 |

◆□ > ◆□ > ◆ Ξ > ◆ Ξ > → Ξ → のへで

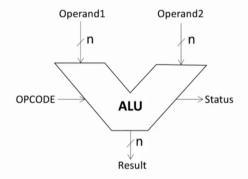

# Arithmetic and Logic Unit (ALU)

▲□▶ ▲□▶ ▲□▶ ▲□▶ □ のQで

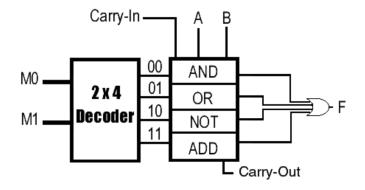

## Constructing an ALU

▲□▶ ▲圖▶ ▲画▶ ▲画▶ 三回 ●の≪で

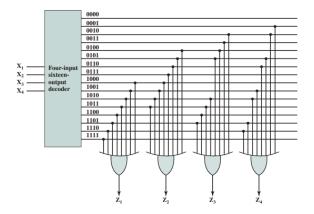

# Memory in Combinational Circuits

- These circuits can also have memory

- The kind is called read-only memory (ROM)

- ROM is permanent and created during fabrication

- Outputs are a function of the present inputs

- Can be implemented with a decoder and a set of OR gates

(ロ) (同) (三) (三) (三) (○) (○)

# ROM

| Input |    |       |       |       | Ou    | tput  |       |

|-------|----|-------|-------|-------|-------|-------|-------|

| $X_1$ | X2 | $X_3$ | $X_4$ | $Z_1$ | $Z_2$ | $Z_3$ | $Z_4$ |

| 0     | 0  | 0     | 0     | 0     | 0     | 0     | 0     |

| 0     | 0  | 0     | 1     | 0     | 0     | 0     | 1     |

| 0     | 0  | 1     | 0     | 0     | 0     | 1     | 1     |

| 0     | 0  | 1     | 1     | 0     | 0     | 1     | 0     |

| 0     | 1  | 0     | 0     | 0     | 1     | 1     | 0     |

| 0     | 1  | 0     | 1     | 0     | 1     | 1     | 1     |

| 0     | 1  | 1     | 0     | 0     | 1     | 0     | 1     |

| 0     | 1  | 1     | 1     | 0     | 1     | 0     | 0     |

| 1     | 0  | 0     | 0     | 1     | 1     | 0     | 0     |

| 1     | 0  | 0     | 1     | 1     | 1     | 0     | 1     |

| 1     | 0  | 1     | 0     | 1     | 1     | 1     | 1     |

| 1     | 0  | 1     | 1     | 1     | 1     | 1     | 0     |

| 1     | 1  | 0     | 0     | 1     | 0     | 1     | 0     |

| 1     | 1  | 0     | 1     | 1     | 0     | 1     | 1     |

| 1     | 1  | 1     | 0     | 1     | 0     | 0     | 1     |

| 1     | 1  | 1     | 1     | 1     | 0     | 0     | 0     |

▲□▶▲圖▶▲≣▶▲≣▶ ≣ のへで

# ROM

・ロト・日本・日本・日本・日本・日本