# Concepts, Structure and Functions

Joannah Nanjekye

July 02, 2024

▲□▶ ▲□▶ ▲□▶ ▲□▶ ▲□ ● のへぐ

**Course Overview**

Concepts

**Functions**

Structure

# Syllabus

- Course resources will be available on D2L

- Also find them here: http://cs.unb.ca/~jnanjeky/teaching/cs3853

- Textbook: W. Stallings, Computer Organization and Architecture, Designing for Performance

- Instructor's website will have more resources than D2L

◆□▶ ◆□▶ ▲□▶ ▲□▶ □ のQ@

#### **Tentative Schedule**

| Week | Lecture Topic                                                                            | Assignment | Quiz | Lab |

|------|------------------------------------------------------------------------------------------|------------|------|-----|

| 1    | Computer evolution and performance                                                       |            |      | ~   |

| 2    | Digital logic, Boolean Algebra, logic<br>gates, combinational and sequential<br>circuits | ~          |      | ~   |

| 3    | Processor architecture and structure                                                     | ~          | ~    | ~   |

| 4    | Memory architecture                                                                      | ~          |      | ~   |

| 5    | Interfacing and I/O strategies                                                           | ~          |      | ~   |

| 6    | Parallelism and parallel organizations,<br>performance enhancements                      |            | ~    |     |

◆□▶ ◆□▶ ◆ □▶ ◆ □▶ ● □ ● ● ● ●

# Delivery

- Lectures

- Assignments (20%)

- Four in total

- No assignment in the first week

#### Read the plagiarism policy

- Quizzes (5%)

- Two in total for 30 minutes

- July 17 and 31

- Read the plagiarism policy

- Labs (35%)

- Wed. 13:00-15:50 PM Head Hall 301 Laboratory

(日) (日) (日) (日) (日) (日) (日)

- You may be asked to present your solution

- Group work is fine

- Individual submissions are required

- Read the plagiarism policy

- Final Exam (40%)

- Monday, Aug. 12, 14:00 17:00

# Delivery

- Email: jnanjeky@unb.ca

- Office Hours: Mon. 11:30 12:30 ITC 321

- You are free to use the internet for more resources

◆□▶ ◆□▶ ▲□▶ ▲□▶ □ のQ@

Accommodations are handled by the registrar

**Architecture** refers to attributes of a system that are visible to a programmer These atributes have direct impact on the logical execution of a program

**Organization** refers to the operational units and their interconnections that realize the architectural specifications

#### Architecture Examples

- Instruction set

- Bit representation for data types

- I/O mechanisms

- Memory addressing techniques

▲□▶ ▲□▶ ▲□▶ ▲□▶ = 三 のへで

# **Organization Examples**

- Control signals

- Interfaces

- Memory technology

◆□ > ◆□ > ◆豆 > ◆豆 > ̄豆 \_ のへで

#### Architecture vs. Organization

#### The distinction is still important

- Architecture is usually more stable:

- IBM System/370 architecture

- Remains in use in the IBM main frames

< □ > < 同 > < Ξ > < Ξ > < Ξ > < Ξ < </p>

- Organization keeps changing to appeal to:

- Frequency of use

- Speed

- Cost and size

#### Structure: The way in which the components are interrelated

# **Function:** The operation of each individual component as part of the structure

▲□▶ ▲□▶ ▲ 三▶ ▲ 三▶ - 三 - のへぐ

#### The Von Neumann Computer Model

◆□▶ ◆□▶ ◆□▶ ◆□▶ ● □ ● ● ● ●

## Features of the Von Neumann Architecture

- 1. The most common computer model

- 2. This model uses the stored program concept where:

- Memory holds the program

- And the data the instructions act on

- 3. Memory is addressed by location numbers (addresses) not the type of the contents

◆□▶ ◆□▶ ▲□▶ ▲□▶ ■ ののの

4. Execution and memory accessed is sequential/linear

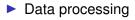

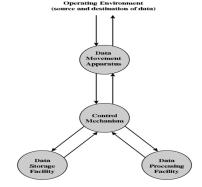

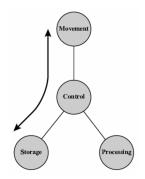

# Functions of a Computer

A computer has four core functions

- Data storage

- Data movement

- Control

▲□▶▲□▶▲□▶▲□▶ □ のQ@

# Control

- Monitors and manages computer's resources

- Maintains the operation of the functional components according to instructions

- Put simply the control unit orchestrates control of data processing, data storage, and data movement

< □ > < 同 > < Ξ > < Ξ > < Ξ > < Ξ < </p>

## Data Movement

- The computer operating environment has data sources and destinations

- Data movement is in two forms:

- input/output: when data is moved from a directly connected device, called a peripheral

- Data Communication: when data is moved from a long distance or remote device

◆□▶ ◆□▶ ◆□▶ ◆□▶ ● ● ● ●

# Storage

- Data storage is useful for all forms of life times:

- Short Term: temporary storage for immediate processing like temporary and loop variables

- Long Term: non-temporary storage of data for subsequent access e.g. logging and data records

◆□▶ ◆□▶ ◆□▶ ◆□▶ ● ● ● ●

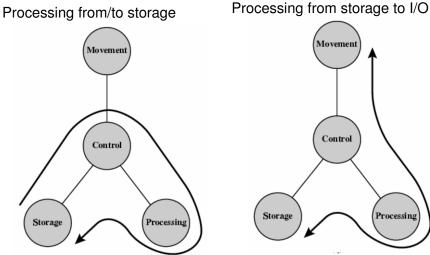

## **Data Processing**

- This is a core function of the computer

- Processing is achieved with arithmetic and logical operations performed on data

- There are different mechanisms of data processing

(ロ) (同) (三) (三) (三) (○) (○)

# Data Processing

▲□▶ ▲□▶ ▲ 三▶ ▲ 三▶ - 三 - のへぐ

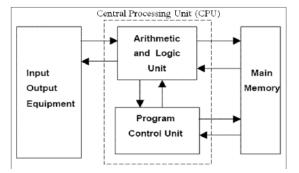

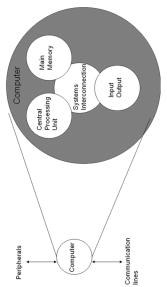

# **Computer Structure**

A computer has four main components

- Central Processing Unit (CPU): Known as a processor, responsible for controlling computer operations and performs data processing functions

- Main Memory: stores data

- Input/Output: Moves data between the computer and external environment

- System Interconnection: Achieves communication among CPU, main memory, and I/O, e.g. system bus

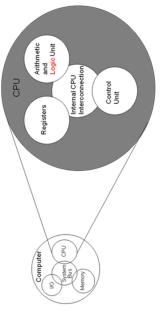

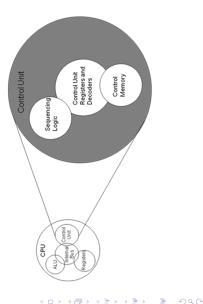

# **Central Processing Unit**

- Control Unit: controls CPU operation which eventually controls the computer

- Arithmetic and Logic Unit (ALU): Performs data processing functions

- Registers: Provide CPU internal storage

- CPU Interconnection: Achieves communication among control unit, ALU and registers

# **Control Unit**

- Implementation of the control unit can vary

- The approach used in this example is the *microprogramming* approach

- Where microinstructions define the functionality of the control unit

#### **Multicore Structure**

- Consists of multiple processors residing on a single chip, multicore computers

- Each processing unit is called a core

- Terminology:

- Central Processing Unit (CPU): consists of ALU. control unit and registers. This unit fetches and executes instructions

- Core: An individual processing unit on a processor unit. Equivalent to a CPU of a single-CPU computer

- Processor: A physical piece of silicon consisting of one or several cores.

(ロ) (同) (三) (三) (三) (○) (○)

#### Components in a Multicore Structure

◆□▶ ◆□▶ ◆ □▶ ◆ □▶ ─ □ ─ ○ < ○

#### Cache

- Cache memory refers to multiple layers of memory between the processor and main memory

- Cache is faster and smaller than main memory

- It is used to to speed up main memory by storing data from main memory

< □ > < 同 > < Ξ > < Ξ > < Ξ > < Ξ < </p>

- Cache memory is used to store data that is likely to be accessed in the near future

- There are multiple levels of cache:

- level 1 (L1)

- level 2 (L2)

- level 3 (L3)

- L (n) is smaller and faster than L (n + 1)

#### Components of a Core

- Instruction Logic: Fetches instructions, decodes the instructions to determine the operation and the memory locations of associated operands

- Arithmetic and Logic Unit (ALU): Executes the operation specified by an instruction

(ロ) (同) (三) (三) (三) (○) (○)

Load/Store Logic: Manages the movement of data between main memory via the cache

#### Lecture Resources